### NATIONAL UNIVERSITY OF SCIENCE AND TECHNOLOGY FACULTY OF INDUSTRIAL TECHNOLOGY BACHELOR OF ENGINEERING DEGREE DURATION 3 HOURS – JANUARY 2011

# TEE 2111 DIGITAL ELECTRONICS

# INSTRUCTIONS TO CANDIDATES

- 1. ANSWER ALL QUESTIONS

- 2. SHOW YOUR STEPS CLEARLY IN CALCULATIONS

- 3. START THE ANSWER FOR EACH QUESTION ON A FRESH PAGE

#### **QUESTION ONE**

Convert the following numbers:

- a) 68780053<sub>10</sub> into a binary number

- b) 123754018 into a hexa-decimal number

- c) 111010101010011.11101<sub>2</sub> into a decimal number

- d) 0.84765<sub>10</sub> into an octal number

- e) 9DEC154<sub>16</sub> into an octal number

[10 points]

### **OUESTION TWO**

Perform the following binary arithmetic operations:

- a) Add 10101111012 and 111001110012

- b) Divide 1001001 9100102 by 1100102

- c) Use 1s complements to subtract 1011011000101.1012 from 10101100110.1112

- d) Use 2s complements to subtract 10011001.11<sub>2</sub> from 11000111000111.101<sub>2</sub>

[16 points]

# **QUESTION THREE**

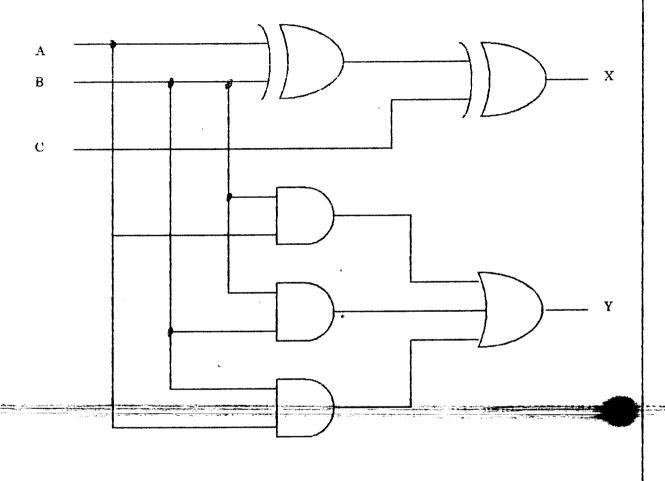

Redraw the circuit shown in Figure 1 using 2-input NAND gates only.

Figure 1

[8 points]

#### **QUESTION FOUR**

Consider the output Y in Table 1.

- a) Write the logic equation for the function Y as logic sum of AND terms

- b) Minimize the expression using Boolean algebra theorems.

- c) Convert the minimized expression from (c) so that the circuit is implemented on NOR gates only.

- d) Draw the circuit diagram

[20 points]

Table 1

| A | В | C | D   | Y  | Z    |

|---|---|---|-----|----|------|

| 0 | 0 | 0 | 0   | 1  | 0    |

| 0 | 0 | 0 | 1   | 1  | 1    |

| 0 | 0 | 1 | 0   | 0  | 1    |

|   | 0 | 1 | 1   | 0  | 0    |

| 0 | 1 | 0 | 0   | 1  | 1    |

| 0 | 1 | 0 | 1   | 0  | 0    |

| 0 | 1 | 1 | 0   | 1  | Х    |

| 0 | 1 | 1 | .1  | 0  | 0    |

| 1 | 0 | 0 | 0   | 1  | 1    |

| 1 | 0 | 0 | 1   | 0_ | X    |

| 1 | 0 | 1 | 0   | 1  | ايرا |

| 1 | 0 | 1 | 1   | 1  | 0    |

| 1 | 1 | 0 | 0   | 0  | 0    |

| 1 | 1 | 0 | 1 ' | 1  | X    |

| 1 | 1 | 1 | 0   | 0  | 0    |

| 1 | 1 | 1 | 1   | 1  | 1    |

#### **QUESTION FIVE**

Consider the output Z in Table 1.

- a) Write the logic equation for the function Z in canonical form.

- b) Transfer the expression for Z on a Karnaugh Map

- c) Minimize the expression.

- d) Convert the minimized expression from (c) so that the circuit is implemented on NAND gates only.

- e) Draw the circuit diagram.

[16 points]

#### **QUESTION SIX**

Using the circuit diagram of a full adder, show the full circuit diagram of an adder that will add two 3-bit numbers.

[10 points]

#### **QUESTION SEVEN**

A logic function F is given with the following expression:

$$F(A,B,C,D) = \sum (0,1,2,4,6,8,13,14)$$

.

Use a 4-to-one multiplexer to implement the logic function [10 points]

# **QUESTION EIGHT**

Design a binary-to-octal decoder circuit. Only one output at time should be at logic 1 indicating the binary code at the inputs.

Draw the circuit diagram.

[10 points]