# Drawe to Oracle Internal

### ATIONAL UNIVERSITY OF SCIENCE AND TECHNOLOGY

## FACULTY OF SCIENCE AND TECHNOLOGY EDUCATION DIGITAL ELECTRONICS

#### PTE2254

**MAIN Second Semester Examination Paper**

May 2019

This examination paper consists of 4 pages

Time allowed: 3 hours

**Total Marks: 100**

Special requirements: NONE

Examiner's name: Mrs D. Chasokela

**INSTRUCTIONS**

1. The paper has 4 printed pages.

- 2. Each question carries 25 marks.

- 3. Answer question 1 and any 3 questions.

- 4. Start your answer for each question on a fresh page.

#### **MARK ALLOCATION**

| QUESTION | MARKS |

|----------|-------|

| 1.       | 25    |

| 2.       | 25    |

| 3        | 25    |

| 4.       | 25    |

| 5.       | 25    |

| TOTAL    | 100   |

Page 1 of 3

Copyright: National University of Science and Technology 2019 PTE2254

#### **QUESTION 1**

(a) Represent an XOR gate using symbol, truth table and equivalent circuit diagram.

[9 marks]

(b) Convert the following:

| (i) 133 <sub>8</sub> to decimal equivalent     | (ii) 91 <sub>10</sub> to octal equivalent |

|------------------------------------------------|-------------------------------------------|

| (iii) 24,68 to decimal equivalent              | (iv) 423 <sub>10</sub> to Hex equivalent  |

| (v) Hex 9F2 <sub>16</sub> to binary equivalent | 10111101 <sub>2</sub> to octal equivalent |

| 21,125 <sub>10</sub> to binary equivalent      | 37 <sub>10</sub> to binary equivalent     |

| 101112+100102                                  | 10111 <sub>2</sub> ×101 <sub>2</sub>      |

| 0,00112+0,11102                                | 1110 <sub>2</sub> ×111 <sub>2</sub>       |

| 1010112-100102                                 | $11001_2 \div 101_2$                      |

| 11012-10112                                    | 1110011 <sub>2</sub> ÷101 <sub>2</sub>    |

[16 marks]

#### **QUESTION 2**

Illustrate a BCD 7 segment decoder using a block diagram and a truth table. [25 marks]

#### **QUESTION 3**

(a) A + B = A + A + B [5 marks]

(b) (A+B)(A+C)=A+BC [5 marks]

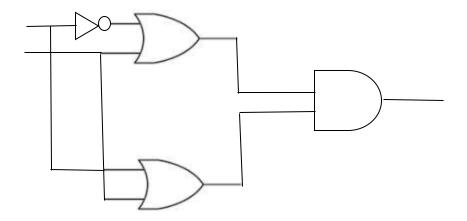

(c) Draw a logic circuit to implement the expression  $X=A B + \overline{B} C$  [5 marks]

(d) Represent logic 0 and 1 in possible states of a circuit. [10 marks]

Page 1 of 3

#### **QUESTION 4**

- (a) A truth table with variables ABC and output D has output 0, 0, 1, 1, 0, 1, 0, 1. Create a truth table and represent the Boolean equation using a Karnaugh Map. [10 marks]

- (b) Simplify the following in Boolean form:

(i)

$$Y = [\overline{(A + B)} \cdot C.\overline{D}]$$

[5 marks]

(ii)

$$Y = A B \overline{C} + A \overline{B} \overline{C}$$

[5 marks]

(iii)

[5 marks]

#### **QUESTION 5**

Draw and explain an SR Latch flip flop.

[25 marks]

#### **END OF EXAMINATION**

Page 1 of 3

Copyright: National University of Science and Technology 2019 PTE2254